「東海エリア 電気電子 技術セミナー」

東海モノづくり企業を支える無料技術セミナー

|

2025年4月~第3木曜日2025年度WEB技術セミナー セミナー開催時間 10:15~12:00 (受付時間: 09:45) 無料で受講できます

各社 定員500名

|

|---|

|

HOME > Ⅲ.実装・レイアウトを考慮した基板設計のポイント > 電子回路基板における勘所

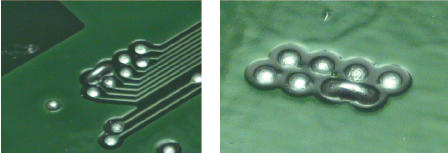

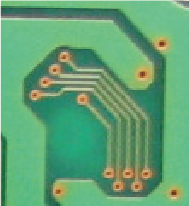

電子回路基板における勘所

Ⅲ.実装・レイアウトを考慮した

|

|

第91回2025年9月18日(木)

第91回2025年9月18日(木)